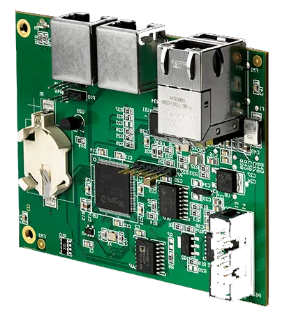

High-density boards with the highest signal integrity

Sierra Electrotek is always pushing the limits of HDI PCB fabrication to offer the smallest trace and space and via sizes. OEMs across all industries come to us for our fine line capabilities and high yields.

-

Down to 2-mil trace and space

-

Down to 2-mil holes

-

Via-in-pad technology

-

Electrical testing

-

10% impedance tolerance

-

IPC Class 3/ES

The

PLUS

Because we know how tricky it can be to build the perfect HDI PCB stack-up, our engineering team offers help and evaluate your files. Reach out to us for assistance.

Give us a call or send us an email to get

started on your project.